# SG384 RF Signal Generator

# User Manual

# Certification

Stanford Research Systems certifies that this product met its published specifications at the time of shipment.

# Warranty

This Stanford Research Systems product is warranted against defects in materials and workmanship for a period of one (1) year from the date of shipment.

# Service

For warranty service or repair, this product must be returned to a Stanford Research Systems authorized service facility. Contact Stanford Research Systems or an authorized representative before returning this product for repair.

Information in this document is subject to change without notice.

Copyright © Stanford Research Systems, Inc., 2011. All rights reserved.

Stanford Research Systems, Inc. 1290-C Reamwood Avenue Sunnyvale, California 94089 Phone: (408) 744-9040 Fax: (408) 744-9049 <u>www.thinkSRS.com</u>

Printed in the U.S

# Contents

| Contents                               | i        |

|----------------------------------------|----------|

| Safety and Preparation for Use         | vii      |

| Symbols You May Find on SRS Products   | viii     |

| Specifications                         | ix       |

| Quick Start Instructions               | xvii     |

| Introduction                           | 1        |

| Feature Overview                       | 1        |

| Waveform Overview                      | 3        |

| Spectral Overview                      | 5        |

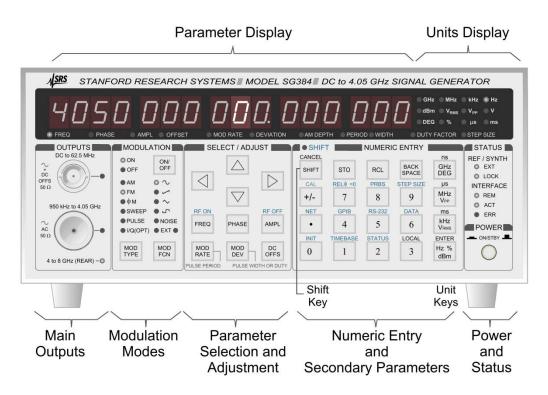

| Front-Panel Overview                   | 7        |

| Parameter and Units Display            | 7        |

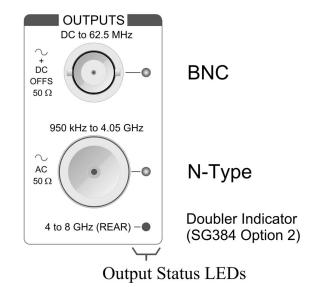

| Main Output                            | 8        |

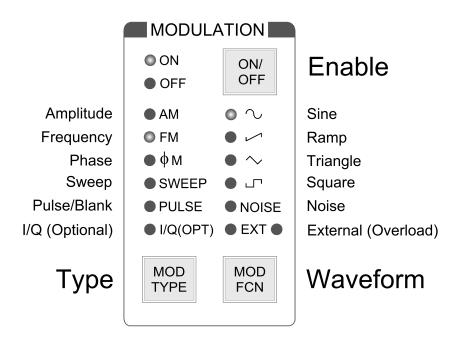

| Modulation Modes                       | 9        |

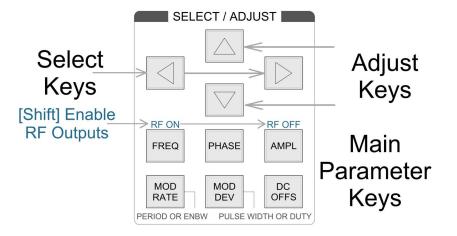

| Parameter Selection and Adjustment     | 10       |

| Numeric Entry and Secondary Parameters | 11       |

| Power and Status                       | 15       |

| Rear-Panel Overview                    | 16       |

| AC Power                               | 16       |

| Timebase                               | 16       |

| Remote Interfaces                      | 17       |

| GPIB<br>DD 000                         | 17       |

| RS-232                                 | 17       |

| Ethernet<br>Modulation                 | 17<br>17 |

| Rear-Panel Optional Outputs            | 18       |

| Option 1: Clock Outputs                | 18       |

| Option 2: 8 GHz Frequency Doubler      | 18       |

| Option 3: I/Q Modulator                | 18       |

|                                   | Table of Contents | i |

|-----------------------------------|-------------------|---|

| peration                          | 19                |   |

| Introduction                      | 19                |   |

| Power-On                          | 19                |   |

| Synthesizer and Outputs           | 20                |   |

| Setting Parameters                | 20                |   |

| Frequency                         | 21                |   |

| Phase                             | 21                |   |

| Amplitude and Power               | 22                |   |

| DC Offset                         | 23                |   |

| RF ON/RF OFF                      | 24                |   |

| Sweeps and Modulation             | 25                |   |

| Introduction                      | 25                |   |

| Modulation Rate                   | 25                |   |

| Modulation Deviation              | 25                |   |

| Modulation Pane                   | 26                |   |

| Modulation On/Off                 | 26                |   |

| Modulation Type                   | 26                |   |

| Modulation Function               | 26                |   |

| Modulation Sources and Outputs    | 27                |   |

| Linear Modulation                 | 27                |   |

| Pulse Modulation                  | 27                |   |

| Noise Modulation                  | 28                |   |

| Internal Modulation Source        | 28                |   |

| Amplitude Modulation              | 29                |   |

| Frequency Modulation              | 31                |   |

| Phase Modulation                  | 35                |   |

| Pulse and Blank Modulation        | 37                |   |

| Phase Continuous Frequency Sweeps | 39                |   |

| I/Q Modulation (Optional)         | 41                |   |

| Secondary (Shift) Parameters      | 45                |   |

| REL Φ=0                           | 45                |   |

| PRBS                              | 45                |   |

| STEP SIZE                         | 45                |   |

| Timebase                          | 46                |   |

| NET                               | 46                |   |

| GPIB                              | 48                |   |

| RS-232                            | 49                |   |

| DATA                              | 49                |   |

| STATUS                            | 50                |   |

| LOCAL                             | 51                |   |

| INIT                              | 51                |   |

| CAL                               | 51                |   |

| Factory Default Settings          | 52                |   |

|                                | Table of Contents |  |

|--------------------------------|-------------------|--|

| mote Programming               | 55                |  |

| Introduction                   | 55                |  |

| Interface Configuration        | 55                |  |

| GPIB                           | 56                |  |

| RS-232                         | 56                |  |

| LAN                            | 57                |  |

| Network Security               | 58                |  |

| Front-Panel Indicators         | 58                |  |

| Command Syntax                 | 59                |  |

| Parameter Conventions          | 60                |  |

| Numeric Conventions            | 60                |  |

| Abridged Index of Commands     | 61                |  |

| Detailed Command List          | 63                |  |

| Common IEEE-488.2 Commands     | 63                |  |

| Status and Display Commands    | 66                |  |

| Signal Synthesis Commands      | 69                |  |

| Modulation Commands            | 72                |  |

| List Commands                  | 78                |  |

| Interface Commands             | 79                |  |

| Status Byte Definitions        | 81                |  |

| Serial Poll Status Byte        | 81                |  |

| Standard Event Status Register | 82                |  |

| Instrument Status Register     | 82                |  |

| List Mode                      | 83                |  |

| List Instrument States         | 83                |  |

| Enables/Disables               | 84                |  |

| Modulation List States         | 85                |  |

| Error Codes                    | 87                |  |

| Execution Errors               | 87                |  |

| Query Errors                   | 88                |  |

| Device Dependent Errors        | 88                |  |

| Parsing Errors                 | 89                |  |

| Communication Errors           | 90                |  |

| Other Errors                   | 90                |  |

| Example Programming Code       | 91                |  |

|                                              | Table of Contents | iv |

|----------------------------------------------|-------------------|----|

| Circuit Description                          | 95                |    |

| Overview                                     | 95                |    |

| Block Diagram                                | 95                |    |

| Detailed Circuit Description                 | 97                |    |

| Front-Panel Display                          | 98                |    |

| Front-Panel Display Shield                   | 98                |    |

| Motherboard                                  | 99                |    |

| Timebases                                    | 99                |    |

| LF DDS and 19 MHz Reference                  | 100               |    |

| Microcontroller and Interface                | 101               |    |

| Modulation Processor                         | 102               |    |

| Modulation ADC and DACs                      | 103               |    |

| RF DDS                                       | 104               |    |

| RF Block and Rear-Panel Options Interface    | 105               |    |

| Power Conditioning                           | 106               |    |

| Motherboard to RF Block Jumper               | 106               |    |

| RF Output Block                              | 106               |    |

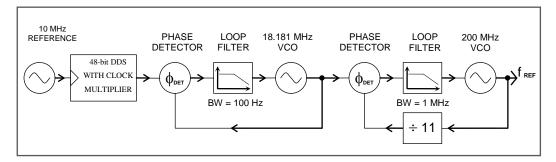

| RF Synthesizer                               | 107               |    |

| RF Dividers and Selectors                    | 108               |    |

| RF I/Q Modulator, Amplifiers and Attenuators | 109               |    |

| RF Output Attenuators                        | 110               |    |

| BNC Output                                   | 110               |    |

| Power Supply                                 | 111               |    |

| Rear-Panel Options                           | 112               |    |

| Clock Output (Options 1)                     | 112               |    |

| RF Doubler (Option 2)                        | 113               |    |

| I/Q Modulator (Option 3)                     | 114               |    |

| Timebase Options                             | 114               |    |

| Appendix A : Rational Approximation S        | Synthesis 115     |    |

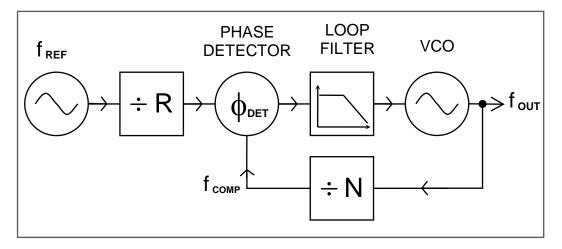

| Phase Lock Loop Frequency Synthesizers       | 115               |    |

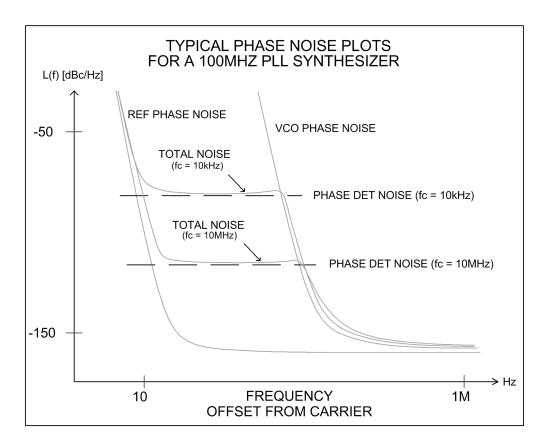

| Phase Noise                                  | 116               |    |

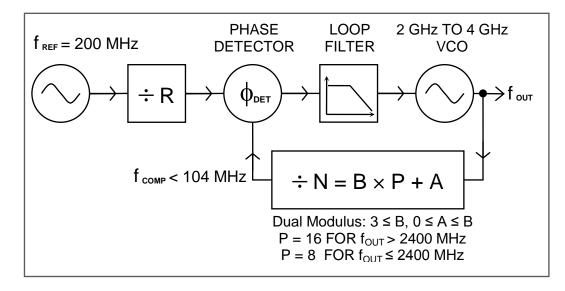

| Increasing Frequency Resolution              | 117               |    |

| A Note on Fractional-N Synthesis             | 117               |    |

| About YIG Oscillators                        | 117               |    |

|                                              | 118               |    |

| A New Approach<br>An Example                 | 110               |    |

| Elimination of Error                         | 120               |    |

| Conclusion                                   | 120               |    |

| Outousion                                    | 120               |    |

|                                                           | Table of Contents | V |

|-----------------------------------------------------------|-------------------|---|

| Appendix B : Parts List                                   | 121               |   |

| Front-Panel Display (Assemblies 320)                      | 123               |   |

| Front-Panel EMI Filter (Assembly 324)                     | 124               |   |

| Motherboard (Assembly 322)                                | 125               |   |

| RF to Motherboard Jumper (Assembly 329)                   | 132               |   |

| RF Synthesizer (Assembly 327)                             | 133               |   |

| RF Output (Assembly 328)                                  | 136               |   |

| Power Supply (Assembly 337)                               | 138               |   |

| Clock and 4 to 8 GHz Doubler (Option 1 & 2) (Assembly 332 | 2) 139            |   |

| IQ Modulator (Option 3) (Assembly 335)                    | 141               |   |

| OCXO Timebase (Assembly 605)                              | 142               |   |

| Rubidium Timebase (Option 4) (Assembly 607)               | 142               |   |

| Chassis (Assembly 336)                                    | 142               |   |

| Appendix C : SG384 Schematic List                         | 143               |   |

| Schematic 1: Block Diagram                                | 145               |   |

| Schematic 2: Front Panel Display                          | 146               |   |

| Schematic 3: Display EMI Filter                           | 147               |   |

| Schematic 4: Mother Board 1, Frequency Refs               | 148               |   |

| Schematic 5: Mother Board 2, 19 MHz Ref                   | 149               |   |

| Schematic 6: Mother Board 3, CPU                          | 150               |   |

| Schematic 7: Mother Board 4, Modulation Processor         | 151               |   |

| Schematic 8: Mother Board 5, Modulation ADC / DACs        | 152               |   |

| Schematic 9: Mother Board 6, RF Reference                 | 153               |   |

| Schematic 10: Mother Board 7, Interface                   | 154               |   |

| Schematic 11: Mother Board 8, Power Supplies              | 155               |   |

| Schematic 12: Mother Board to RF Jumper                   | 156               |   |

| Schematic 13: Synthesizer 1, 2-4 GHz and Control          | 157               |   |

| Schematic 14: Synthesizer 2, Dividers and LPF             | 158               |   |

| Schematic 15: Output 1, Attenuation & Controls            | 159               |   |

| Schematic 16: Output 2, RF Stage                          | 160               |   |

| Schematic 17: Output 3, BNC                               | 161               |   |

| Schematic 18: Power Supply                                | 162               |   |

| Schematic 19: Rear Panel Option Jumper                    | 163               |   |

| Schematic 20: Option #1 Clock Outputs                     | 164               |   |

| Schematic 21: Option #2 4-8 GHz Doubler                   | 165               |   |

| Schematic 22: Option #3 I/Q Modulator                     | 166               |   |

| Schematic 23: Timebase Adaptor Interface                  | 167               |   |

| Revisions                                                 | 169               |   |

# Safety and Preparation for Use

## Line Voltage

The SG384 operates from a 90 to 132  $V_{AC}$  or 175 to 264  $V_{AC}$  power source having a line frequency between 47 and 63 Hz. Power consumption is less than 90 VA total. In standby mode, power is turned off to the main board. However, power is maintained at all times to the installed timebase. Units with standard ovenized quartz oscillator or optional rubidium timebase will consume less than 15 VA and 25 VA, respectively, in standby mode.

## **Power Entry Module**

A power entry module, labeled AC POWER on the back panel of the SG384, provides connection to the power source and to a protective ground.

#### **Power Cord**

The SG384 package includes a detachable, three-wire power cord for connection to the power source and protective ground.

The exposed metal parts of the box are connected to the power ground to protect against electrical shock. Always use an outlet which has a properly connected protective ground. Consult with an electrician if necessary.

## Grounding

BNC shields are connected to the chassis ground and the AC power source ground via the power cord. Do not apply any voltage to the shield.

## Line Fuse

The line fuse is internal to the instrument and may not be serviced by the user.

## **Operate Only with Covers in Place**

To avoid personal injury, do not remove the product covers or panels. Do not operate the product without all covers and panels in place.

## **Serviceable Parts**

The SG384 does not include any user serviceable parts. Refer service to a qualified technician.

# Symbols You May Find on SRS Products

| Symbol        | Description                              |

|---------------|------------------------------------------|

| $\sim$        | Alternating Current                      |

|               | Caution – risk of electrical shock       |

| $\rightarrow$ | Frame or Chassis terminal                |

|               | Caution – refer to accompanying document |

|               | Earth (ground) terminal                  |

|               | Battery                                  |

| $\sim$        | Fuse                                     |

|               | Power On                                 |

|               | Power Off                                |

| Ċ             | Power Standby                            |

# **Specifications**

#### Frequency Setting (f<sub>C</sub>)

| Frequency ranges          |                                                    |

|---------------------------|----------------------------------------------------|

| BNC output                | DC to 62.5 MHz                                     |

| N-type output             | 950 kHz to 4.05 GHz                                |

| SMA rear-panel (Option 2) | 4.05 GHz to 8.1 GHz                                |

| Frequency resolution      | 1 μHz at any frequency                             |

| Switching speed           | <8 ms (to within 1 ppm)                            |

| Frequency error           | $<(10^{-18} + \text{timebase error}) \times f_{C}$ |

| Frequency stability       | $<1:10^{-11}$ (1 second Allan variance)            |

|                           |                                                    |

#### Spectral Purity of the RF Output Referenced to 1GHz<sup>(1)</sup>

| Sub harmonics                                  | None (No doublers are used below 4 GHz.)             |

|------------------------------------------------|------------------------------------------------------|

| Harmonics                                      | <-25 dBc with <+7 dBm on N-Type output               |

| Spurious                                       |                                                      |

| offsets from carrier                           |                                                      |

| <10 kHz                                        | <-65 dBc                                             |

| $\geq 10 \text{ kHz}$                          | <-75 dBc                                             |

| Phase noise                                    |                                                      |

| Offset from carrier                            | Phase Noise (typical)                                |

| 10 Hz                                          | -80 dBc/Hz                                           |

| 1 kHz                                          | -102 dBc/Hz                                          |

| 20 kHz                                         | -116 dBc/Hz                                          |

| 1 MHz                                          | -130 dBc/Hz                                          |

| Residual FM                                    | 1 Hz rms, typical, over 300 Hz to 3 kHz bandwidth    |

| Residual AM                                    | 0.006 % rms, typical, over 300 Hz to 3 kHz bandwidth |

| <sup>(1)</sup> Spurs, phase noise and residual | FM scale by 6 dB/octave to other carrier frequencies |

#### **Phase Setting of Front-Panel Outputs**

| Phase range      | ±360 ° |

|------------------|--------|

| Phase resolution |        |

| DC to 100 MHz    | 0.01°  |

| 100 MHz to 1 GHz | 0.1°   |

| 1 GHz to 8.1 GHz | 1.0°   |

#### **Timebase Input**

| Frequency       | 10 MHz, ±2 ppm                        |

|-----------------|---------------------------------------|

| Amplitude       | 0.5 to 4 $V_{PP}$ (-2 dBm to +16 dBm) |

| Input impedance | 50 $\Omega$ , AC coupled              |

#### **Timebase Output**

| Frequency | 10 MHz, sine                                    |

|-----------|-------------------------------------------------|

| Source    | 50 $\Omega$ , DC transformer coupled            |

| Amplitude | $1.75 V_{PP} \pm 10 \% (8.8 \pm 1 \text{ dBm})$ |

#### Standard OCXO Timebase

| Oscillator type |  |

|-----------------|--|

| Stability       |  |

| Aging           |  |

Oven controlled, 3<sup>rd</sup> OT, SC-cut crystal <0.002 ppm (0 to 45°C) <0.05 ppm/year

# Rubidium Timebase (Option 4)

| Oscillator type | Oven controlled, 3 <sup>rd</sup> OT, SC-cut crystal |

|-----------------|-----------------------------------------------------|

| Physics package | Rubidium vapor frequency discriminator              |

| Stability       | <0.0001 ppm (0 to 45°C)                             |

| Aging           | <0.001 ppm/year                                     |

#### Front-Panel BNC Output (50 Ω load)

| Frequency range        | DC to 62.5 MHz                               |

|------------------------|----------------------------------------------|

| Amplitude              |                                              |

| Specified              | 1.00 to 0.001 $V_{RMS}$ (+13 dBm to -47 dBm) |

| Allowed <sup>(1)</sup> | to 1.25 V <sub>RMS</sub> (+14.96 dBm)        |

| Offset                 | $\pm 1.5 \text{ V}_{\text{DC}}$              |

| Maximum excursion      | $\pm 1.42$ V (amplitude + offset)            |

| Amplitude resolution   | <1 %                                         |

| Amplitude accuracy     | ±5 %                                         |

| Offset resolution      | 5 mV                                         |

| Harmonics              | <-40 dBc                                     |

| Spurious               | <-75 dBc                                     |

| Output coupling        | DC, 50 $\Omega \pm 2$ %                      |

| User load              | $50 \Omega$                                  |

| Reverse protection     | $\pm 5 \text{ V}_{\text{DC}}$                |

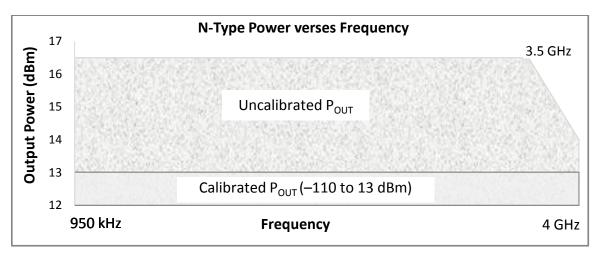

#### Front-Panel N-type Output (50 Ω load)

| Frequency range        | 950 kHz to 4.05 GHz                                           |

|------------------------|---------------------------------------------------------------|

| Power output           |                                                               |

| Specified              | +13 dBm to -110 dBm                                           |

| Allowed <sup>(1)</sup> | 16.5 dBm                                                      |

| Voltage output         |                                                               |

| Specified              | $1 \text{ V}_{\text{RMS}}$ to 0.7 $\mu \text{V}_{\text{RMS}}$ |

| Allowed <sup>(1)</sup> | 1.5 V <sub>RMS</sub>                                          |

| Power resolution       | 0.01 dBm                                                      |

| Power accuracy         | $\pm 1 \text{ dB}$                                            |

| Output coupling        | 50 Ω, AC                                                      |

| User load              | 50 Ω                                                          |

| VSWR                   | <1.6                                                          |

| Reverse protection     | $30 V_{DC}$ , +25 dBm RF                                      |

<sup>(1)</sup> Allowed power setting for which specifications are not guaranteed

#### **Internal Modulation Source**

Sine, ramp, saw, square, pulse, noise -80 dBc (typical at 20 kHz) <0.05 % (1 kHz)

1  $\mu$ Hz to 500 kHz 1  $\mu$ Hz to 50 kHz 1  $\mu$ Hz <1:2<sup>31</sup> + timebase error White Gaussian noise, RMS = DEV / 5 1  $\mu$ Hz < ENBW < 50 kHz 1  $\mu$ s to 10 s 100 ns to 9999.9999 ms 5 ns PRBS length 2<sup>5</sup> to 2<sup>19</sup>. Bit period (100 + n.5) ns 100 ns to 10 s in 5 ns steps

#### **Modulation Waveform Output**

| Output impedance | 50 $\Omega$ (for reverse termination) |

|------------------|---------------------------------------|

| User load        | Unterminated 50 $\Omega$ coax         |

| AM, FM, ΦM       | $\pm 1$ V for $\pm$ full deviation    |

| Pulse/Blank      | "Low" = 0 V, "High" = $3.3 V_{DC}$    |

| Connector        | Rear-panel BNC                        |

#### **External Modulation Input**

Modes Unmodulated level AM, FM, ΦM Modulation bandwidth Modulation distortion Input impedance Input Coupling Input offset Pulse/Blank threshold Connector AM, FM,  $\Phi$ M, Pulse and Blank 0 V input for unmodulated carrier  $\pm 1$  V input for  $\pm$  full deviation >100 kHz <-50 dB 100 k $\Omega$ AC (4 Hz) or DC <500  $\mu$ V +1 V<sub>DC</sub> Rear-panel BNC

#### **Frequency Modulation**

| Frequency deviation              |                                                                                           |

|----------------------------------|-------------------------------------------------------------------------------------------|

| Minimum                          | 0.1 Hz                                                                                    |

| Maximum                          |                                                                                           |

| $f_C \leq 126.5625 \text{ MHz}$  | 1 MHz                                                                                     |

| $f_C \le 253.1250 \text{ MHz}$   | 2 MHz                                                                                     |

| $f_C \le 506.25 \text{ MHz}$     | 4 MHz                                                                                     |

| $f_C \le 1.0125 \text{ GHz}$     | 6 MHz                                                                                     |

| $f_C \le 2.025 \text{ GHz}$      | 16 MHz                                                                                    |

| $f_C \le 4.050 \text{ GHz}$      | 32 MHz                                                                                    |

| $f_C \le 8.100 \text{ GHz}$      | 64 MHz                                                                                    |

| Deviation resolution             | 0.1 Hz                                                                                    |

| Deviation accuracy               |                                                                                           |

| $f_C \le 62.5 \text{ MHz}$       | <0.1 %                                                                                    |

| $f_C > 62.5 \text{ MHz}$         | <3 %                                                                                      |

| Modulation source                | Internal or external                                                                      |

| Modulation distortion            | $<-70 \text{ dB} (f_{C} = 1 \text{ GHz}, f_{M} = 20 \text{ kHz}, f_{D} = 20 \text{ kHz})$ |

| Ext FM carrier offset            | <1:1000 of deviation                                                                      |

| Modulation bandwidth             |                                                                                           |

| $f_{\rm C} \le 62.5 \text{ MHz}$ | 500 kHz                                                                                   |

| $f_{\rm C} > 62.5$ MHZ           | 100 kHz                                                                                   |

#### **Phase Continuous Frequency Sweeps**

| Frequency span<br>Sweep ranges | 0.1 Hz to entire sweep range<br>DC to 62.5 MHz<br>59.375 to 128.125 MHz<br>118.75 to 256.25 MHz<br>237.5 to 512.5 MHz<br>475 to 1025 MHz<br>950 to 2050 MHz<br>1900 to 4100 MHz |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation resolution           | 3800 to 8200 MHz (Opt. 2 only)<br>0.1 Hz                                                                                                                                        |

| Sweep source                   | Internal or external                                                                                                                                                            |

| Sweep distortion               | <0.1 Hz + (deviation / 1000)                                                                                                                                                    |

| Sweep offset                   | <1:1000 of deviation                                                                                                                                                            |

| Sweep function                 | Triangle, ramps, or sine up to 120 Hz                                                                                                                                           |

#### Phase Modulation

| 0 to 360°                                                                                |

|------------------------------------------------------------------------------------------|

|                                                                                          |

| 0.01°                                                                                    |

| 0.1°                                                                                     |

| 1.0°                                                                                     |

|                                                                                          |

| <0.1 %                                                                                   |

| <3 %                                                                                     |

| Internal or external                                                                     |

| $<-70 \text{ dB} (f_{C} = 1 \text{ GHz}, f_{M} = 20 \text{ kHz}, \Phi_{D} = 90^{\circ})$ |

|                                                                                          |

| 500 kHz                                                                                  |

| 100 kHz                                                                                  |

|                                                                                          |

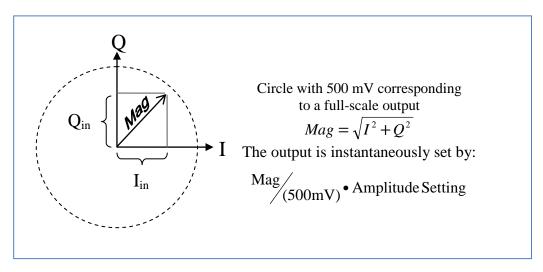

# External I/Q Modulation (Option 3)

| Carrier Frequency Range | Operates on $400 \text{ MHz} \le f_C \le 4.05 \text{ GHz}$ |

|-------------------------|------------------------------------------------------------|

| Modulated output        | Front-panel N-type only (+10 dBm max)                      |

| I/Q inputs              | 50 $\Omega$ , $\pm 0.5$ V, (rear BNCs)                     |

| I or Q input offset     | <500 μV                                                    |

| I/Q full scale          | $(I^2 + Q^2)^{1/2} = 0.5 V$                                |

| Carrier suppression     | >40 dBc                                                    |

| Modulation bandwidth    | 100 MHz                                                    |

#### **Amplitude Modulation**

| Range                                               | 0 to 100 % (Decreases above +7 dBm output) |

|-----------------------------------------------------|--------------------------------------------|

| Resolution                                          | 0.1 %                                      |

| Modulation source                                   | Internal or external                       |

| Modulation distortion ( $f_M = 1$ kHz, Depth = 50%) |                                            |

| $f_C \le 62.5$ MHz, BNC output                      | <1 %                                       |

| $f_C > 62.5$ MHz, N-type output                     | <3 % typical                               |

| Modulation bandwidth                                | >100 kHz                                   |

#### **Pulse/Blank Modulation**

| Pulse mode         | Logic "high" turns BNC and RF on               |

|--------------------|------------------------------------------------|

| Blank mode         | Logic "high" turns BNC and RF off              |

| On/Off ratio       |                                                |

| N-Type             |                                                |

| 1 to 4 GHz         | 40 dB                                          |

| Less than 1 GHz    | 60 dB                                          |

| BNC                | 70 dB                                          |

| Pulse feed-through | 10 % of carrier for 20 ns at turn-on (typical) |

| Turn on/off delay  | 60 ns                                          |

| RF rise/fall time  | 20 ns                                          |

| Modulation source  | Internal or external pulse                     |

#### Square Wave Clock Outputs (Option 1)

| Differential clocks<br>Frequency range<br>Transition time | Rear-panel SMAs drive 50 $\Omega$ loads<br>DC to 4.05 GHz<br><35 ps (20 % to 80 %) |

|-----------------------------------------------------------|------------------------------------------------------------------------------------|

| Jitter                                                    | < 35 ps (20 % to 80 %)                                                             |

| $F_{\rm C}$ > 62.5 MHz                                    | <300 fs rms (1 kHz to 5 MHz BW)                                                    |

| $F_{C} \le 62.5 \text{ MHz}$                              | <10 <sup>-4</sup> U.I. rms                                                         |

| Amplitude                                                 | 0.4 to 1.0 $V_{PP}$                                                                |

| Offset                                                    | $\pm 2 \text{ V}_{\text{DC}}$                                                      |

| Amplitude & Offset resolution                             | 5 mV                                                                               |

| Amplitude & Offset accuracy                               | ±5 %                                                                               |

| Output coupling                                           | DC, 50 $\Omega \pm 2$ %                                                            |

| Compliance                                                | ECL, PECL, RSECL, CML & LVDS                                                       |

#### **RF** Doubler Output (Option 2)

| Output                                         | Rear-panel SMA                       |  |

|------------------------------------------------|--------------------------------------|--|

| Frequency range                                | 4.05 to 8.10 GHz                     |  |

| RF amplitude                                   |                                      |  |

| 4.05 to 7 GHz                                  | -10  dBm to +13  dBm                 |  |

| 7 to 8.10 GHz                                  | -10  dBm to  +7  dBm                 |  |

| Allowed <sup>(2)</sup>                         | +16.5 dBm                            |  |

| Sub harmonic $(f_C / 2)$                       |                                      |  |

| $f_{\rm C}$ < 6.5 GHz                          | <-25 dBc typical                     |  |

| $f_{\rm C} = 8.1 \text{ GHz}$                  | <-12 dBc typical                     |  |

| Mixing products $(2f_C \text{ and } 3f_C / 2)$ | <-20 dBc                             |  |

| Harmonics $(n \times f_C)$                     | <-25 dBc                             |  |

| Spurious (8 GHz)                               | <-55 dBc ( $> 10$ kHz offset)        |  |

| Phase noise (8 GHz)                            | –98 dBc/Hz at 20 kHz offset, typical |  |

| Amplitude resolution                           | 0.01 dBm                             |  |

| Amplitude accuracy                             |                                      |  |

| 4.05 to 6.5 GHz                                | ±1 dB                                |  |

| 6.5 to 8.10 GHz                                | $\pm 2 \text{ dB}$                   |  |

| Modulation modes                               | FM, $\Phi$ M, and Sweeps             |  |

| Output coupling                                | ΑC, 50 Ω                             |  |

| Reverse protection                             | 30 V <sub>DC</sub> , +25 dBm RF      |  |

| <sup>(2)</sup> Allowed power setting for which | n specifications are not guaranteed  |  |

|                                                |                                      |  |

#### DC Bias Source (comes with Option 2)

| Output            | Rear-panel SMA |

|-------------------|----------------|

| Voltage range     | ±10 V          |

| Offset voltage    | <20 mV         |

| DC accuracy       | ±0.2 %         |

| DC resolution     | 5 mV           |

| Output resistance | 50 Ω           |

| Current limit     | 20 mA          |

#### **Computer Interfaces (all are standard)**

| Ethernet (LAN) | 10/100 Base-T. TCP/IP & DHCP default. |

|----------------|---------------------------------------|

| GPIB           | IEEE-488.2                            |

| RS-232         | 4.8k-115.2k baud, RTS/CTS flow        |

#### General

| Line power<br>EMI Compliance | <90 W, 90 to 264 V <sub>AC</sub> , 47 to 63 Hz with PFC FCC Part 15 (Class B), CISPR-22 (Class B) |

|------------------------------|---------------------------------------------------------------------------------------------------|

| Dimensions                   | $8.5^{\circ} \times 3.5^{\circ} \times 13^{\circ} (W \times H \times D)$                          |

| Weight                       | <10 lbs                                                                                           |

| Warranty                     | One year on parts and labor                                                                       |

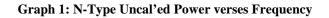

**Graph 2: Single Sideband Phase Noise**

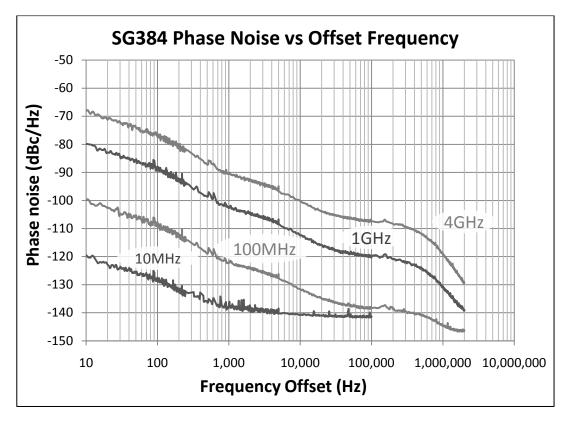

Graph 3: Single Sideband Phase Noise for RF PLL Modes

# **Quick Start Instructions**

## Step by Step Example

With the power button in the Standby position, connect the SG384 to a grounded outlet using the power cord provided.

- (1) On the SG384

- (a) Push in the POWER button to turn on the unit.

- (b) Load default settings by pressing the key sequence : [SHIFT] [ 0 ] [Hz % dBm]

- (2) On the oscilloscope

- (a) Set channel 1 for 200 mV / division, 50  $\Omega$  input termination

- (b) Set the time scale to 100 ns / division

- (c) Connect the SG384 BNC output to the oscilloscope channel 1

- (d) Set the trigger for AC, rising edge, channel 1 and adjust threshold as necessary

- (i) There should be a sine wave with ten cycles shown of 630 mV  $_{PP}$  (corresponding to 1 mW into 50  $\Omega$  or 0 dBm).

- (3) On the SG384

- (a) Press the [FREQ] key

- (i) Press the SELECT  $\triangleleft$  key three times to select the 1 MHz digit.

- (ii) Press the  $\nabla$  key five times to change the frequency to 5 MHz

- (iii) The display should now have five cycles shown.

- (b) Press key sequence [ 2 ] [MHz]

- (i) The oscilloscope should show two cycles of a sine wave.

- (4) On the SG384

- (a) Press [AMPL] repeatedly until the 'BNC' menu is displayed

- (i) Press key sequence [+/–][ 6 ][dBm]

- (b) The oscilloscope will now have a sine wave of 315  $mV_{\mbox{\scriptsize PP}}$

Refer to the detailed instructions that follow for more information on the operation of the SG384.

# Introduction

# **Feature Overview**

The SG384 Signal Generator is a high precision DC to 4 GHz (8 GHz with installation of option 2) synthesizer. The advance modulation capabilities, bandwidth, and precision of the SG384 make it an ideal instrument for many applications. The intuitive and efficient front panel allows direct entry of parameters.

The SG384 builds upon three generations of instruments at SRS:

- 1) The DS3xx series of DDS based Synthesized Function Generator provides a conceptual base for certain aspects of the SG384 offering rich modulation sources and DDS based waveform generation, precision RF outputs, as well as an established and widely accepted user interface.

- 2) The CG635 Synthesized Clock Generator provides a basis for the synthesis architecture utilized in the SG384, allowing a very high degree of frequency precision while simultaneously providing low phase noise and spurious content.

- 3) Finally, the DG645 Digital Delay Generator provided a base platform of software, microprocessor, and Field Programmable Gate Arrays allowing the SG384 to implement real-time instrument functions that can be dynamically modified to meet complex requirements for the different operating modes in a time and cost efficient manner. The SG384 is also built upon a proven and tested software, firmware, and user interface model.

Various new technologies have also been leveraged to realize the SG384 — some of these include very high frequency DDS chips ( $\geq 1$  GHz), larger FPGAs supporting DSP operations, and utilization of RF components that are cost effective and technically mature.

One area involves a novel new approach to Direct Digital Synthesis called Rational Approximation Synthesis (please see the appendix on page 168 for a detailed explanation).

All of these taken together allow the realization of the high performance, cost competitive, and functionally rich SG384 Synthesizer operating from DC to 8 GHz.

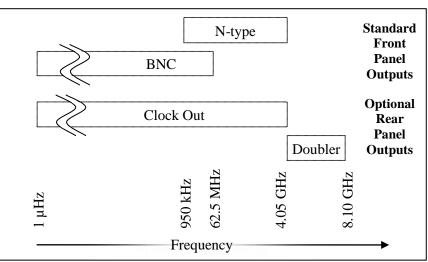

The SG384's front panel provides two separate outputs. A Type-N connector provides frequencies from 950 kHz to 4.05 GHz with powers (amplitudes) of -110 to +13 dBm (0.707  $\mu V_{RMS}$  to 1  $V_{RMS}$ ). The BNC connector provides frequencies from 1  $\mu$ Hz to 62.5 MHz with powers (amplitudes) from -47 to +13 dBm (1 mV<sub>RMS</sub> to 1 V<sub>RMS</sub>). Both the Type-N and BNC allow for output typical powers (amplitudes) of up to 16.5 dBm (1.5 V<sub>RMS</sub>) at relaxed signal specifications.

The SG384's user interface allows direct access to all of the main synthesizer functions, with lesser used functions assigned to secondary (or shifted) keys.

The rear panel provides additional functionality including an input for an external 10 MHz timebase, a modulation interface, and various optional interfaces, including outputs that extend the operation up to 8.10 GHz. GPIB, RS-232, and Ethernet are standard.

The SG384 may be operated as a single tone CW synthesizer for crystal clear frequency generation. For a 1 GHz output the SG384 has -75 dBc of SFDR and a single sideband phase noise of less than -116 dBc / Hz at 20 kHz offset from carrier. The SG384 has a frequency resolution of 1  $\mu$ Hz with accuracies of 0.002 ppm using the standard OCXO. With an optional rubidium timebase the accuracy is increased to 0.0001 ppm.

The standard SG384 also supports a wide range of modulation functions — AM, FM,  $\Phi$ M, Pulse, and Noise. The technology utilized allows for broad modulation deviations and rates with very low distortion products. Option 3 allows I/Q modulation.

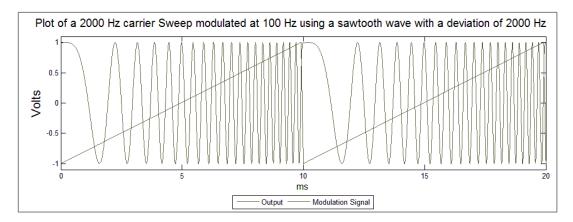

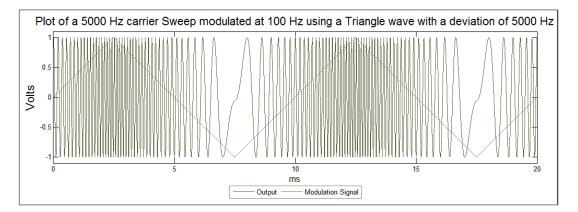

The SG384 supports frequency sweeps for the characterization of networks and other analysis. The sweep spans are frequency dependent. For frequencies greater than 62.5 MHz, sweep spans are set on octave boundaries (62.5 to 125 MHz, 125 to 250 MHz, etc.). For frequencies below 62.5 MHz, sweeps can span the entire range (DC to 62.5 MHz). The SG384 allows sweep rates up to 120 Hz, with saw tooth, triangle, or sin sweeps supported.

The rear panel has a frequency doubler option to extend the frequency operating range to 8.1 GHz with powers (amplitudes) from -10 to +13 dBm (70.7 mV<sub>RMS</sub> to 1.0 V<sub>RMS</sub>).

The rear panel also supports optional differential clock outputs. These operate over frequencies from 1µHz to 4.05 GHz. They replicate the synthesized frequency with edge transitions of less than 35 ps, programmable amplitude of 0.4 to 1 V<sub>PP</sub>, and offsets of  $\pm 2$  V<sub>DC</sub>.

# **Waveform Overview**

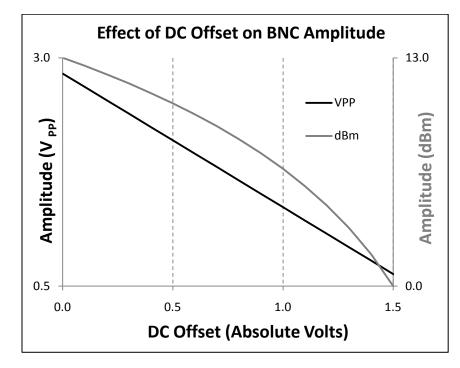

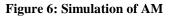

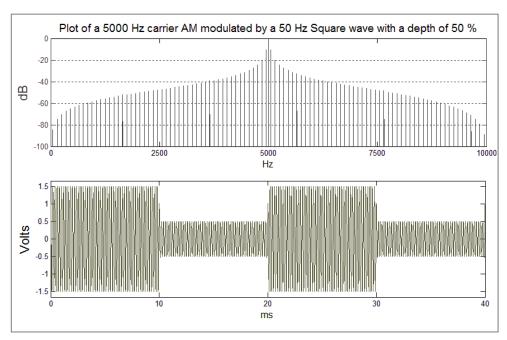

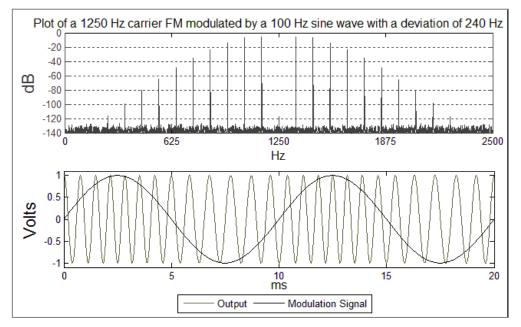

The following waveforms and spectral plots demonstrate some of the SG384's capabilities:

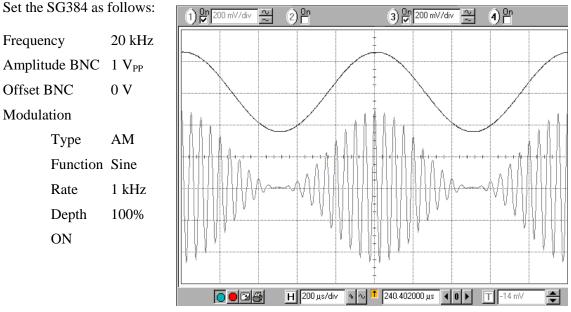

Waveform 1 is a 20 kHz carrier being amplitude modulated by a 1 kHz sine wave. The top trace is the rear panel Modulation output, while the bottom trace is the front-panel BNC output:

Waveform 1: AM Modulation

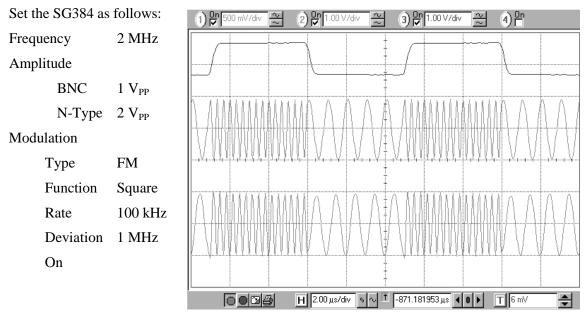

In Waveform 2, the internal modulator is set to FM between 1 MHz and 3 MHz with a 100 kHz square wave. The top trace is the real panel Modulation output, while the middle and bottom traces are the front panel BNC and N-Type outputs.

Waveform 2: FSK Modulation

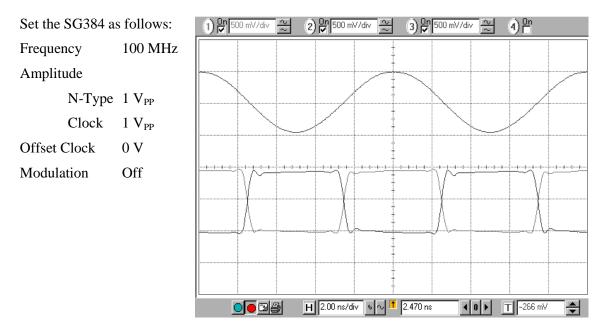

Waveform 3 shows the optional rear panel clock outputs with the frequency set to 100 MHz. The top trace is front panel N-Type output with the differential clock outputs depicted by the lower traces. The displayed transition times are limited by the 1.5 GHz bandwidth of the oscilloscope.

Waveform 3: Clock Outputs

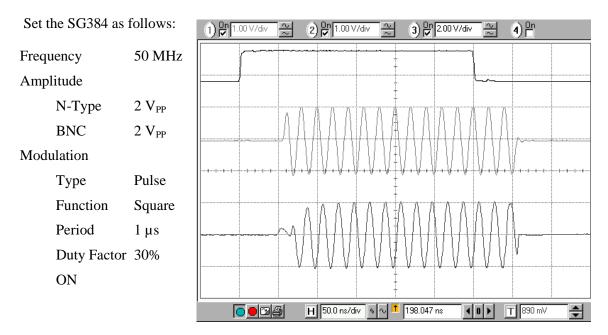

Waveform 4 is a 50 MHz carrier being pulse modulated with a 1 MHz, 300 ns pulse waveform. The upper trace is the timing signal with the middle trace being the BNC output, and the lower trace being the RF output. There are delays of 50 ns in the gating circuitry as shown.

Waveform 4: Pulse Modulated Output

# **Spectral Overview**

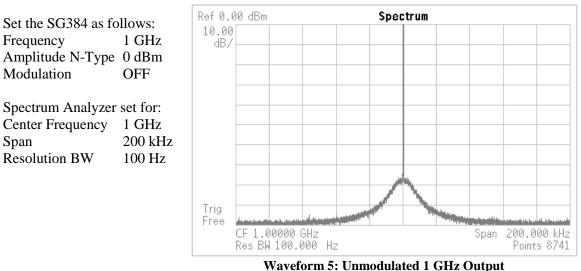

Waveform 5 shows a direct measurement taken on a spectrum analyzer with a 200 kHz span and 100 Hz RBW. The noise floor of the spectrum analyzer dominates over most of the 200 kHz span.

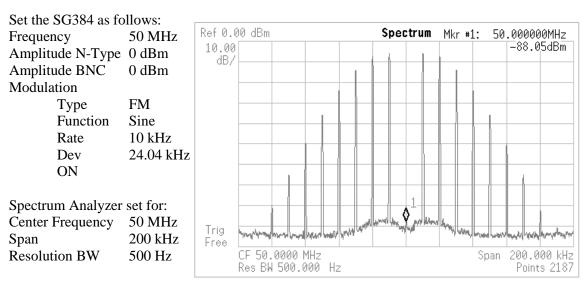

Waveform 6 depicts a 50 MHz carrier frequency modulated at a rate of 10 kHz and a deviation of 24.0477 kHz, for a modulation index  $\beta = 2.40477$ . The carrier amplitude is proportional to the

Bessel function  $J_0(\beta)$  and has its first zero at 2.40477, and thus suppresses the carrier.

Waveform 6: 50 MHz with FM Carrier Suppressed

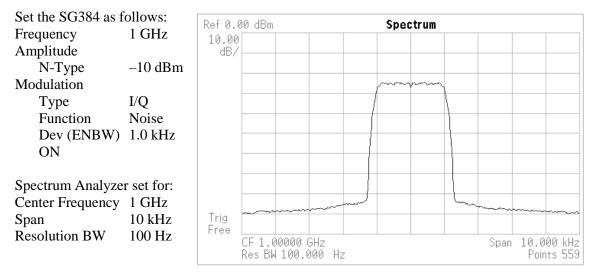

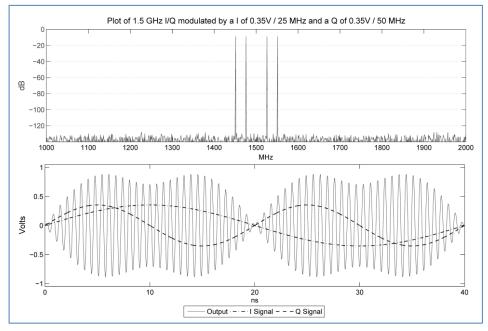

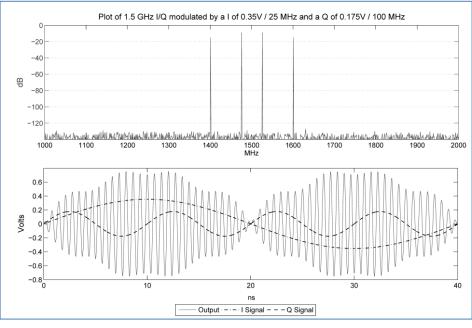

Option 3 allows I/Q modulation for output frequencies from 400 MHz to 4.05 GHz. Two signal sources may be used for modulation: the external I & Q inputs or an internal noise generator. The external I & Q inputs are on the rear panel. The internal noise generator has adjustable noise bandwidth from 1 Hz to 50 kHz. Waveform 7 is a 1 GHz carrier being modulated by the internal noise generator with 1 kHz noise bandwidth.

Waveform 7: I/Q Modulation using internal noise source

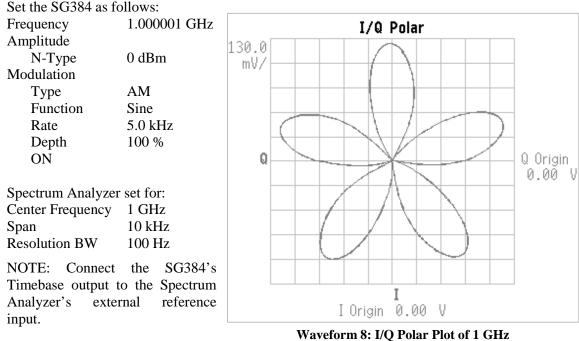

An unmodulated carrier at the analyzer's reference frequency (1 GHz in this case) appears as a single dot in the I/Q plane. When the carrier frequency is offset, the single dot moves in a circle about the center of the I/Q plane. The pattern shown occurs when the carrier amplitude is modulated with 100 % depth at a rate of five times the carrier offset frequency (creating five lobes). The symmetry of the lobes indicates that there is no residual phase distortion (AM to  $\Phi$ M conversion) in the amplitude modulator. The narrow line of the trajectory is indicative of low phase and amplitude noise.

Waveform 8: I/Q Polar Plot of 1 Gl Referenced to 1.000001 GHz AM of 5 kHz at 100 %

# **Front-Panel Overview**

Figure 1: The SG384 Front Panel

The power switch is located in the lower right corner of the front panel. Pushing the switch enables power to the instrument. Pushing the switch again places the instrument in stand-by mode, where power is enabled only to the internal timebase.

The front panel is divided into seven sections (or "Panes"): Parameter Display, Units Display, OUTPUTS, MODULATION, SELECT/ADJUST, NUMERIC ENTRY, and STATUS.

# **Parameter and Units Display**

The SG384 has a sixteen digit display showing the value of the currently displayed parameter. The LEDs below the display indicate which parameter is being viewed. Error messages may also appear in the display, briefly.

The Units Display highlights the units associated with a parameter. Note that a given parameter may have multiple views. For example, the RF output amplitude may be viewed in units of dBm,  $V_{RMS}$ , or  $V_{PP}$ .

# **Main Output**

These are the synthesizer's main signal outputs. Two types of connectors are provided due to the bandwidths covered by the instrument.

## **BNC** Output

Signals on this connector are active for frequency settings between DC and 62.5 MHz. The amplitude may be set independently for levels from 1 mV<sub>RMS</sub> to 1 V<sub>RMS</sub> (-47 dBm to 13 dBm). Increase amplitude setting of 1.5 V<sub>RMS</sub> (16.5 dBm) are allowed with relaxed signal specifications. Additionally, the BNC output may be offset by  $\pm$  1.5 V<sub>DC</sub>.

NOTE: The BNC output is protected against externally applied voltages of up to  $\pm$  5 V.

# N-Type Output

Signals on this connector are active for frequency settings between 950 kHz and 4.05 GHz. The amplitude may be set independently for levels from -110 dBm to 13 dBm (0.7  $\mu V_{RMS}$  to 1  $V_{RMS}$ ). Increase amplitude settings of 16.5 dBm (1.5  $V_{RMS}$ ) are allowed with relaxed signal specifications.

NOTE: The N-type output is protected against externally applied voltages of up to 30  $V_{DC}$  and RF powers up to +25 dBm.

#### Indicators

Three LEDs are used to indicate which of the outputs are active: BNC, N-Type, and the 4 to 8 GHz (REAR) Doubler.

The Doubler LED is lit only when Option 2 is installed and when the frequency is greater than 4.05 GHz.

# **Modulation Modes**

The Modulation pane displays the present modulation state and enables the user to control both the type and function of the modulation.

The [ON/OFF] key enables modulation.

The [MOD TYPE] key allows selection of the type of modulation (via the ADJUST  $\triangle$  and  $\nabla$  keys). The types of modulation available are AM, FM,  $\Phi$ M, Sweep, and Pulse. IQ modulation is available as an option.

The [MOD FCN] key allows the selection of the modulation waveform (via the ADJUST  $\triangle$  and  $\nabla$  keys). The available waveforms include sine, ramp, triangle, square wave, and noise.

The rear panel external modulation input can also be used in either for AM, FM,  $\Phi$ M or Pulse. When the external source is selected, the signal level is monitored. If the external source exceeds operational limits the overload LED turns on and remains on until the condition is removed.

# **Parameter Selection and Adjustment**

# **Display Navigation**

The SELECT/ADJUST section determines which main parameter is shown on the front panel display. The six basic displays for viewing and modifying instrument settings are shown in Table 1. Each display is activated by pressing the correspondingly labeled key.

| Label    | Value Shown in Main Display When Pressed           |

|----------|----------------------------------------------------|

| FREQ     | Current Frequency (f <sub>c</sub> )                |

| PHASE    | Current Phase                                      |

| AMPL     | Current Amplitude – sequences through outputs      |

| DC OFFS  | Current Offset – sequences through the outputs     |

| MOD RATE | Current Modulation Rate (Pulse Period or ENBW)     |

| MOD DEV  | Current Modulation Deviation (Pulse Width or Duty) |

Table 1: SG384 Main Parameter Keys

For Parameter menus with multiple items, repeatedly pressing the Parameter key allows cycling through all of its parameters. For example, in the default configuration multiple key presses of the [AMPL] key will cycle through the various available outputs BNC, Clock, and N-Type.

Some of the parameters will have a blinking digit (the cursor). The cursor indicates which digit will be modified when the ADJUST  $\triangle$  and  $\nabla$  keys are pressed. The SELECT  $\triangleleft$  and  $\triangleright$  keys allow adjusting the cursor for the desired resolution (the step size may also us the shifted function to allow numeric entry).

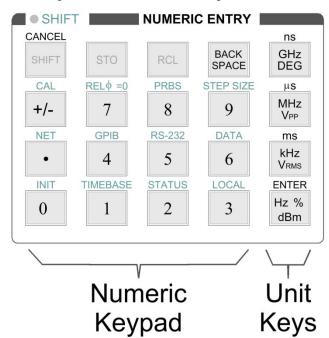

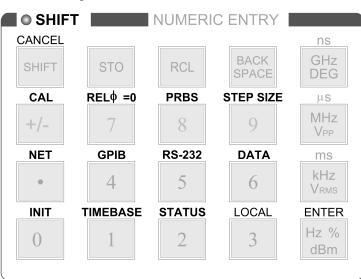

# **Numeric Entry and Secondary Parameters**

This pane is used for changing the currently displayed numeric parameter directly. A parameter is entered numerically and completed by pressing any of the unit keys. Corrections can be made using the BACK SPACE or the entire entry may be aborted by pressing the CANCEL key.

For example, to set the frequency to 1.0001 GHz, press the [FREQ] key followed by the key sequence of  $[1][\bullet][0][0][0][1]$  [GHz].

This pane also allows access to secondary (or "Shifted") functions. The secondary functions are listed above the key in light blue text. A secondary function is accessed by first pressing the SHIFT key (indicated by the SHIFT LED being on) followed by pressing the desired secondary function key.

For example, to set the incremental value for frequency to 12 kHz press [FREQ] [SHIFT] [STEP SIZE], followed by the sequence [1][2][kHz].

Numeric or SHIFT entries may be aborted at any time by pressing the CANCEL key.

## **Stepping Up and Down**

Most instrument settings can be stepped up or down by a programmed amount. The blinking digit identifies the current cursor position and step size. The cursor shows the digit that will change if the parameter is incremented or decremented via the ADJUST keys. Pressing the ADJUST  $\triangle$  ( $\nabla$ ) key causes the displayed parameter to increment (decrement).

# Step Size

Pressing the ADJUST  $\triangle$  and  $\bigtriangledown$  keys increments or decrements the value of the selected digit on the numeric display (to change the selected digit use the SELECT  $\triangleleft$  and  $\triangleright$  keys). To view the step size use the SHIFT [9] (STEP SIZE).

The step size can be changed using the numeric keypad followed by the appropriate unit. To set the step size to an arbitrary value use the SHIFT [9] the enter the desired step size followed by the appropriate unit type. For example, to change the frequency's step size to 1.25 MHz, first press [Shift] then [9] followed by 1.25 and finally the [MHz] unit key. When the cursor is changed to another digit (using the SELECT  $\triangleleft$  or  $\triangleright$  keys) the step size returns to its default value.

# **Store and Recall Settings**

The [STO] and [RCL] keys are for storing and recalling instrument settings, respectively. Instrument settings include modulation configuration and all associated step sizes. Up to nine different instrument settings may be stored in the locations 1 to 9. To save the current settings to location 5, press the keys [STO], [5], [ENTER], sequentially. To recall instrument settings from location 5, press the keys [RCL], [5], [ENTER] sequentially. Note: the INIT key is used to recall default instrument settings. See Default Factory Settings in the Operations chapter on page 52 for a list of default settings.

#### **Secondary Functions**

Many of the keys in the MODIFY section have secondary functions associated with them. The secondary functions are listed above the keys. The [5] key, for example, has RS-232 above it. The meaning of the secondary functions is summarized in Table 2.

| Label     | Primary<br>Key | Function Description                                                              |

|-----------|----------------|-----------------------------------------------------------------------------------|

| CAL       | +/-            | Adjust the timebase, and selects the PLL filter mode                              |

| REL Φ =0  | 7              | Defines the current phase to be 0 degrees and displays phase                      |

| PRBS      | 8              | Allows access to the length of the Pseudo-Random<br>Binary Sequence generator     |

| STEP SIZE | 9              | Set the incremental value used by the ADJUST keys                                 |

| NET       | •              | Configure the Ethernet interface                                                  |

| GPIB      | 4              | Configure the GPIB interface                                                      |

| RS-232    | 5              | Configure the RS-232 interface                                                    |

| DATA      | 6              | Display the most recent data received over any of the remote interfaces           |

| INIT      | 0              | Load default instrument settings                                                  |

| TIMEBASE  | 1              | Displays the installed timebase and its status                                    |

| STATUS    | 2              | View TCP/IP (Ethernet), error, or instrument status, as well as running Self-Test |

| LOCAL     | 3              | Go to local. Enables front panel keys if in remote mode.                          |

A more detailed description of each of the secondary functions is given in the Secondary Functions section of the Operation chapter (page 45).

The secondary functions can only be accessed when the shift mode is active, which is indicated by SHIFT LED in the main display. The SHIFT mode can be toggled on and

off by pressing the [SHIFT] key. For example, to configure the PRBS length, press [SHIFT] [8] to access the PRBS secondary function.

For menu items with multi-parameter settings, the SELECT  $\triangleleft$  and  $\triangleright$  keys allow selection of the various menu items. The MODIFY  $\triangle$  and  $\nabla$  keys may be used to modify a parameter. For example, the first option in the NET menu is TCPIP ENABLE/DISABLE. Use the MODIFY  $\triangle$  and  $\nabla$  keys to change the setting as desired. Then press SELECT  $\triangleright$  to move to the next option which is DHCP ENABLE/DISABLE. Continue pressing the SELECT  $\triangleright$  until all TCPIP settings have been configured as desired.

## Cancel

The [SHIFT] key also functions as a general purpose CANCEL key. Any numeric entry, which has not been completed, can be canceled by pressing the [SHIFT] key. Because of the dual role played by the SHIFT key, the user may have to press [SHIFT] twice to reactivate SHIFT mode. The first key press cancels the current action, and the second key press re-activates SHIFT mode.

# **Power and Status**

The Power and Status pane encompass the power switch and displays the status of the timebase and remote interface(s):

## **Status Indicators**

# **REF / SYNTH**

In the upper right portion of the front panel are two groups of LED indicators. The upper group is labeled REF / SYNTH and indicates the status of the internal timebase. The EXT LED indicates that the SG384 has detected an external 10 MHz reference at the timebase input BNC on the rear panel. If detected, the SG384 will attempt to lock its internal clock to the external reference.

The LOCK LED indicates that SG384 has locked its internal frequency synthesizer at the requested frequency. Normally this LED will only extinguish momentarily when the frequency changes or an external timebase is first applied to the rear input. If the LED stays off, it indicates that the SG384 may be unable to lock to the external timebase. This is most commonly caused by the external frequency being offset by more than 2 ppm from 10 MHz.

# INTERFACE

The lower group of LED indicators is labeled INTERFACE. These LEDs indicate the current status of any active remote programming interface (Ethernet, RS-232, or GPIB).

The REM LED turns on when the SG384 is placed in remote mode by one of the remote interfaces. In this mode, all the front panel keys are disabled and the instrument can only be controlled via the remote interface. The user can return to normal, local mode by pressing the [3] key (also labeled [LOCAL]). The ACT LED flashes when a character is received or sent over one of the interfaces. This is helpful when troubleshooting communication problems. If a command received over the remote interface fails to execute due to either a parsing error or an execution error, the ERR LED will turn on. Information about the error is available in the STATUS secondary display.

#### POWER

The power switch has two positions: STANDBY (switch out) and ON (switch in).

In STANDBY mode, power is only supplied to the internal timebase and the power consumption will not exceed 25 watts.

In ON mode, power is supplied to all circuitry but the power consumption will not exceed 90 watts.

# **Rear-Panel Overview**

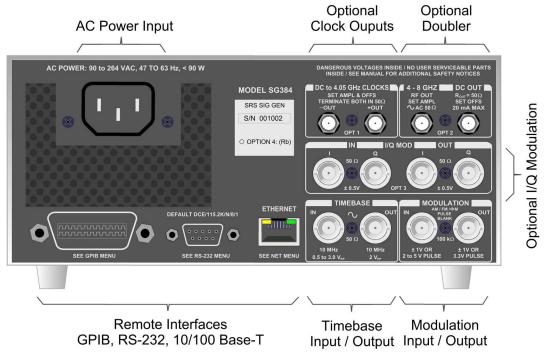

Figure 2: The SG384 Rear Panel

The rear panel provides connectors for AC power, remote computer interfaces, external frequency references, and various additional options.

# **AC Power**

Connect the SG384 to a power source through the power cord provided with the instrument. The center pin is connected to the SG384 chassis so that the entire box is earth grounded.

The SG384 will operate with an AC input from 90 to 264 V, and with a frequency of 47 to 63 Hz. The SG384 requires 90W and implements power factor correction.

Connect the SG384 to a properly grounded outlet. Consult an electrician if necessary.

# Timebase

#### 10 MHz IN

This input accepts an external 10 MHz reference. The external reference should be accurate to at least 2 ppm, and provide a signal of no less than 0.5  $V_{PP}$  while driving a 50  $\Omega$  impedance. The SG384 automatically detects the presence of an external reference, asserting the front panel EXT LED, and locking to it if possible. If the SG384 is unable to lock to the reference, the LOCK LED is turned off.

## 10 MHz OUT

The SG384 also provides a 10 MHz output for referencing other instrumentation to the SG384's high stability OCXO or optional Rubidium Timebase.

## **Remote Interfaces**

The SG384 supports remote control via GPIB, RS-232, or Ethernet. A computer interfaced to the SG384 can perform any operation that is accessible from the front panel. Programming the SG384 is discussed in the Remote Programming chapter on page 55.

Before attempting to communicate with the SG384 over the target interface, please refer to the respective Remote Programming Configuration section on page 55.

#### GPIB

The SG384 comes standard with a GPIB (IEEE-488) communications port for communications over a GPIB bus. The SG384 supports the IEEE-488.1 (1978) interface standard. It also supports the required common commands of the IEEE-488.2 (1987) standard.

#### **RS-232**

The RS-232 port uses a standard 9 pin, female, subminiature-D connector. It is configured as a DCE and supports baud rates from 4.8 kb/s to 115 kb/s. The remaining communication parameters are fixed at 8 Data bits, 1 Stop bit, No Parity, with RTS/CTS configured to support Hardware Flow Control.

#### Ethernet

The Ethernet uses a standard RJ-45 connector to connect to a local area network (LAN) using standard Category-5 or Category-6 cable. It supports both 10 and 100 Base-T Ethernet connection and a variety of TCP/IP configuration methods.

## **Modulation**

#### IN

External modulation is applied to this input. The input impedance is 100 k $\Omega$  with a selectable input coupling of either DC or AC (4 Hz roll off).

For analog modulations (AM, FM,  $\Phi$ M), a signal of  $\pm 1$  V will produce a full scale modulation of the output (depth for AM or deviation for FM and  $\Phi$ M). It supports bandwidths of 100 kHz and introduces distortions of less than -50 dB.

For Pulse/Blank modulation types, this input is used as a discriminator that has a fixed threshold of +1 V.

## OUT

This output replicates the modulation waveform and has a 50  $\Omega$  reverse termination. When using the internal source for AM, FM, and  $\Phi$ M, it provides a waveform determined by the function and rate settings with an amplitude of  $\pm 1 V_{PP}$  into a high impedance. During external analog modulation, this output mirrors the modulation input.

For Pulse modulation, the output is a 3.3V logic waveform that coincides with the gate signal.

## **Rear-Panel Optional Outputs**

Three rear panel options are available on the SG384: a high speed clock outputs, a frequency doubler for extending the SG384's frequency output to 8.1 GHz, and IQ modulator inputs for the N-Type output.

## **Option 1: Clock Outputs**

The clock outputs provide a digital representation of the synthesized signal for frequencies up to 4.05 GHz on a pair of SMA type connectors. The outputs are differential signals with transition times of 35 ps (20 % to 80 %). They are commonly adjustable for amplitudes from 0.40 to 1.00 V, offsets of  $\pm$  2 V, with a resolution of 5 mV.

For frequencies above 62.5 MHz, the jitter on the clock signals will be less than 300 fs with a measurement bandwidth of 5 kHz to 5 MHz. For frequencies below 62.5 MHz the rms jitter will be less than 0.01 %  $\times$  U.I (Unit Interval).

## **Option 2: 8 GHz Frequency Doubler**

This option extends the frequency range of the SG384 to 8.1 GHz with power levels of up to 16.5 dBm. A DC output port is available for providing biasing of external circuits. Both of these signals use SMA type connectors.

## **RF OUT**

This output is operational for frequencies from 4.05 to 8.1 GHz. This output is AC coupled and is adjustable over a range of -10 to +16.5 dBm. The RF output supports FM,  $\Phi$ M, and Swept modulation.

## DC OUT

This output provides DC voltage which is settable over a  $\pm$  10 V range with 5 mV of resolution.

### **Option 3: I/Q Modulator**

This option allows I/Q modulation on the front panel N-Type RF output for output frequencies between 400 MHz and 4.05 GHz.

Either an external source or the internal noise source may be selected.

### I/Q IN

These inputs accept signals of  $\pm 0.5$  V, corresponding to full scale modulation, and have 50  $\Omega$  input impedances. Both inputs support signal bandwidths from DC to 100 MHz.

## I/Q OUT

These outputs duplicate the I/Q modulation waveforms (internally or externally).

All I/Q signals utilize BNC connectors located on the rear panel.

# Operation

# Introduction

The following sections describe the operation of the SG384. The first section describes the basics of setting the frequency, phase, amplitude, and offset. The second section explains sweeps and modulation. The third section explains storing and recalling setups and setting the computer interfaces.

The previous chapter described the function of the front panel keys based on their location on the front panel. This section provides guidelines for viewing and changing instrument parameters independent of their location on the front panel.

## **Power-On**

At power on, the SG384 will briefly display "SG384" followed by the firmware version and the unit serial number. When power on initialization has completed, the SG384 will recall the last known instrument settings from nonvolatile memory.

The SG384 continuously monitors front panel key presses and will save the current instrument settings to nonvolatile memory after approximately five seconds of inactivity. To prevent the nonvolatile memory from wearing out, the SG384 will not automatically save instrument settings that change due to commands executed over the remote interface. The remote commands \*SAV (\*RCL) may be used to explicitly save (recall) instrument settings over the remote interface, if desired. See the SG384 Remote Programming section on page 55 for more information about these commands.

The SG384 can be forced to boot up to factory default settings. This is accomplished by power cycling the unit with the [BACK SPACE] depressed. All instrument settings, except for the remote interface configurations, will be set back to their default values. All calibration bytes will be reset to the values set at the factory at the time of shipment. See the Factory Default Settings section on page 52 for a list of default settings.

## Synthesizer and Outputs

The SELECT/ADJUST pane allows access to the main parameters.

The SG384 operates over a wide range of frequencies. None of the four outputs (including the optional rear panel doubler and clock) operate across the entire frequency range. The associated parameters are inaccessible when the frequency is set outside of an output's operational range. As an example, if the frequency is set for 100 kHz, the N-type and Doubler (if installed) outputs are turned off, and their Amplitude parameters are not accessible.

Figure 3 indicates the operation of the outputs verses frequency. When the frequency is set outside the range of a given output, its associated parameters (Amplitude and Offset) become inaccessible.

Figure 3 - Outputs vs. Frequency

## **Setting Parameters**

The SELECT/ADJUST section determines which parameter is shown in the main front panel display. The six keys for selecting the display of the main instrument settings are shown in Table 3. Each display is activated by pressing the corresponding labeled key.

Table 3: SG384 Main Display Parameters

| Label   | Value                                                     |

|---------|-----------------------------------------------------------|

| FREQ    | Current Frequency (f <sub>c</sub> )                       |

| PHASE   | Current Phase                                             |

| AMPL    | Current Amplitude – sequences through all outputs         |

| DC OFFS | Current Offset – sequences through all outputs            |

| MOD     | Current Modulation Rate (Pulse Period) and ENBW           |

| RATE    |                                                           |

| MOD DEV | Current Modulation Deviation (Pulse Width or Duty Factor) |

## Frequency

Pressing [FREQ] displays the SG384's output frequency and turns on the FREQ LED.

The frequency may be entered in any of the standard units (GHz, MHz, kHz, or Hz). The current display may be normalized to a unit by pressing the desired unit key.

The frequency resolution is 1  $\mu$ Hz at all frequencies. The frequency setting determines which outputs may be active at any given time (see Figure 3 - Outputs vs. Frequency).

# PHASE Phase

FREQ

Pressing [PHASE] displays the SG384's phase and turns on the PHASE LED.

The phase is displayed in degrees and is adjustable over  $\pm$  360°. As the phase exceeds 360°, the parameter is normalized back to zero by setting the display to the new phase modulo 360°.

The phase resolution depends upon the current setting of the frequency. For the frequencies up to 100 MHz the phase resolution is  $0.01^{\circ}$ , with reduced resolution for higher frequencies. Table 4 shows the phase resolution verses frequency:

| Frequency Range  | Phase Resolution |

|------------------|------------------|

| DC to 100 MHz    | 0.01°            |

| 100 MHz to 1 GHz | 0.1°             |

| 1 GHz to 8.1 GHz | 1.0°             |

**Table 4: Phase Resolution**

| SHIFT |

|-------|

| 7     |

In many situations it is useful to be able to normalize the present phase setting to zero. The SG384 allows this using the REL  $\Phi$ =0 function ([SHIFT] [7] keys). This will set the phase parameter to zero, while preserving the current phase.

## **Amplitude and Power**

Pressing [AMPL] displays the SG384's output amplitude or power and turns on the AMPLITUDE LED.

The amplitude has a value for each of the installed outputs, and repeated pressing of [AMPL] sequences through all accessible parameters. Note however, that only those outputs that are active for the current frequency setting will be accessible.

All amplitudes (except for clock) may be displayed in units of dBm,  $V_{RMS}$ , or  $V_{PP}$ , with clock being restricted to  $V_{PP}$ . All stated values assume a load termination of 50  $\Omega$ .

Table 5 lists the range for the various units of the outputs:

|    |         | Calibrated Range<br>Units |                          |                          | Uncal'ed<br>Range <sup>(1)</sup> |

|----|---------|---------------------------|--------------------------|--------------------------|----------------------------------|

|    |         | dBm                       | V <sub>RMS</sub>         | $V_{PP}$                 |                                  |

| T  | N-type  | $-110 \rightarrow +13$    | $0.707\mu \rightarrow 1$ | $2\mu \rightarrow 2.83$  | To 16.5 dBm                      |

| PU | BNC     | $-47 \rightarrow +13$     | $1.00m \rightarrow 1$    | $2.83m \rightarrow 2.83$ | To 15.5 dBm                      |

| LO | Doubler | $-10 \rightarrow +13$     | $0.0707 \rightarrow 1$   | $0.200 \rightarrow 2.83$ | To 16.5 dBm                      |

| ē  | Clock   | N/A                       | N/A                      | $0.4 \rightarrow 1$      | N/A                              |

Table 5: Output Power Range

If an output is set below its minimum value it will be disabled. This is indicated on the display as "off" and by extinguishing the associated output status LED.

(1) Note that the N-Type, BNC, and Doubler outputs support setting the power to an "uncal'ed" region. These output values are typical, and other specifications are not guaranteed for this region. Power levels of 16.5 dBm are achievable.

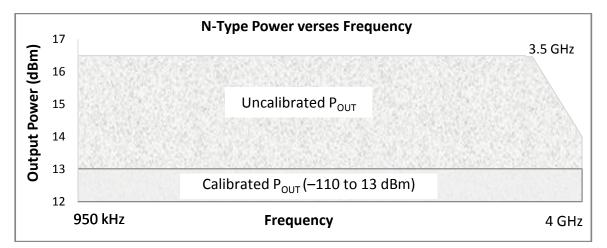

Figure for depicts the region for the N-Type output. The "uncal'ed" output power is reduced above 3.4 GHz to 14 dBm at 4 GHz.

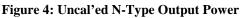

## **DC Offset**

Pressing [DC OFFS] displays the SG384's output offset and turns on DC OFFSET.

The DC offset has values for the BNC as well as some of the installed output options. Repeatedly pressing [DC OFFS] will sequence through all accessible parameters. For SG384's with the optional Doubler, the DC offset associated with the frequency doubler option is always accessible and active.

All DC offsets are displayed in  $V_{DC}$ . Table 6 gives the DC offset range for the various outputs:

| Output         | DC Offset Range |

|----------------|-----------------|

| N-type         | N/A             |

| BNC            | ±1.5V           |

| Rear DC Offset | ±10V            |

| Clock          | $\pm 2V$        |

Table 6: Offset Range

The BNC output will support offsets up to 1.5V. The BNC's maximum instantaneous voltage is limited to 1.9 V. Thus, the output provides 13 dBm (2.828  $V_{PP}$ ) at no offset, and is reduced linearly to 0 dBm (0.632  $V_{PP}$ ) for offsets of ±1.5 V. Figure 5 shows the relationship between BNC amplitude and offset settings.

Figure 5: BNC Output vs. DC Offset

## **RF ON/RF OFF**

FREQ

SHIFT

These are shifted functions of the [FREQ]/[AMPL] keys, respectively.

When the [RF ON]/[RF OFF] are pressed there is a momentary display of "rf on" / "rf off", and the status LEDs for the outputs are set / cleared, respectively.

The [RF OFF] turns off all RF outputs, while setting the clock output to a static "off" state (+OUT to "low", -OUT to "high"). When an output is selected that is off the display will indicate the off status. For example, selecting the N-Type amplitude would display "ntype off".

The [RF ON] returns all RF outputs to their previously active levels.

# **Sweeps and Modulation**

## Introduction

This section describes the SG384's modulation capabilities. The SG384 has powerful and flexible built-in modulation functions, capable of AM, FM,  $\Phi$ M, swept frequency, Pulse, and I/Q modulations. The modulation waveform may be a sine wave, square wave, ramp, triangle wave, noise, or external source. For additional flexibility the SG384 can also quickly cycle through a list of settings with an arbitrary combination of amplitude, frequency, phase, and modulation settings (see List Mode on page 83.)

## **Modulation Rate**

The [MOD RATE] and [MOD DEV] keys are paired in operation and their parameters depend upon the current modulation type and function settings.

Pressing [MOD RATE] displays the SG384's modulation rate associated with the current modulation type and turns on either the MOD RATE (for AM/FM/PM and sweep) or the PERIOD (for pulse/blank) LEDs.

For the standard (AM/FM/ $\Phi$ M) and sweep modulation types, this parameter is the frequency of the applied modulation waveform. The allowable range depends on both the type of modulation and the frequency selected.

For pulse modulation, this selects the period of the pulse. This is settable in 5ns increments from 1  $\mu$ s to 10 s.

For I/Q noise modulation (option 3) this key sets the equivalent noise bandwidth (ENBW) of the modulation

## **Modulation Deviation**

Pressing [MOD DEV] displays the deviation of the current modulation function. Depending on the modulation type, either the MOD DEV, AM DEPTH, WIDTH, or DUTY FACTOR is displayed.

During AM modulation, the AM depth is displayed and corresponds to the peak percentage that the output envelope will span. For example, if the amplitude is set to 1  $V_{PP}$  and the depth is set for 50% the output envelope would span from 0.5 V to 1.5 V.